電源IC輸入端的過應力分析

摘要

電源IC的失效常常是其輸入端受到電氣過應力(EOS)的結果。本文對電源IC輸入端ESD保護單元的結構進行了解釋,說明了它們在受到EOS攻擊時是如何受損的。造成EOS攻擊事件的原因常常是熱插拔和導線或路徑電感與低ESR陶瓷電容結合在一起形成的瞬態效應。在系統設計中採用一些特別的設計可以避免EOS的發生,防範它們可能帶來的危害。

1.

概述

|

在產品研發和生產過程中總是會出現一些IC損壞的現象,要想找出這些IC損壞的根本原因並不總是很容易。有些偶發性的損壞很難被重現,這時的難度就會更大。有些時候IC的失效表現簡直就是災難性的,可能被燒得一塌糊塗,對這樣的狀況進行分析就像要在完全燒成斷垣殘壁的房子裡找出火災的原因一樣,幾乎就是不可能的事情。

立錡科技在長時間的工作中對大量用戶的失效樣品進行了分析。通過對損壞的區域進行仔細的探查,有時候是可以對損壞元件進行準確定位的,這對尋找類似失效的原因會有很大幫助。

在很多情況下,器件失效的原因都是輸入電壓太高了。

本文的後續章節將對Buck轉換器輸入端的結構進行介紹,給出過高的輸入電壓造成器件損壞的機制,通過不同的應用案例說明過高的輸入電壓是如何發生的,還將提供相應的問題解決方案。

|

|

2.

Buck轉換器輸入端的結構

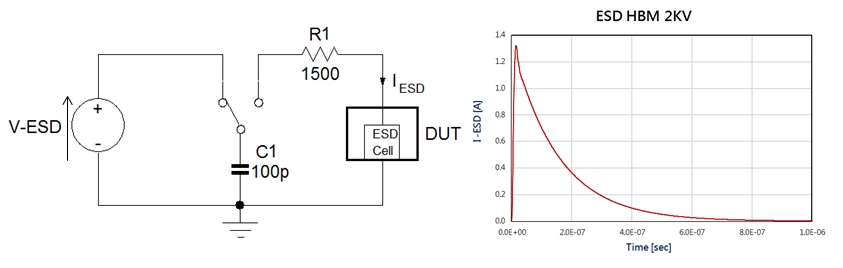

圖1顯示了一個Buck轉換器IC內部的基本構成,其中包含了幾個靜電釋放(ESD)防護單元。

圖1

電源輸入端VIN被一個很大的ESD單元保護著,其保護範圍包括內部穩壓器和MOSFET,因而可以承受很高的靜電電壓。SW端子內部通常沒有ESD單元,因為大型MOSFET本身就可以像ESD保護單元一樣動作,靜電電流可經其體二極體流向GND或VIN端,也可利用它們的擊穿特性實現保護。BOOT端有一個ESD單元處於它和SW之間,其它小信號端子也各有一個小型的ESD單元,它們通常都和輸入串聯電阻一起保護這些小信號端子免受靜電放電的危害。

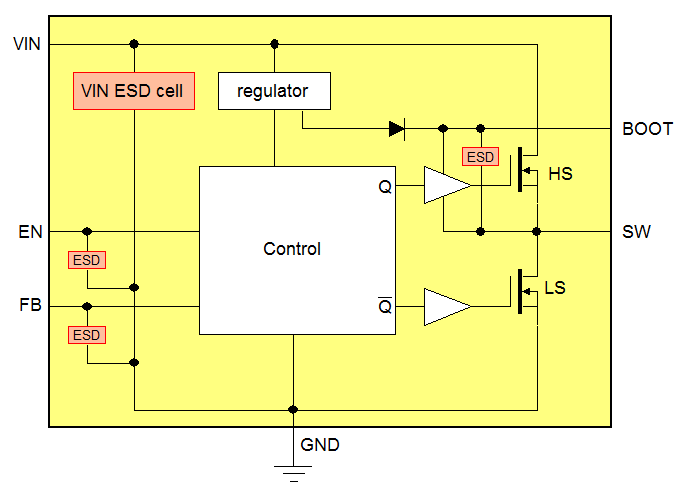

在立錡的電源IC中,用於保護IC端子的ESD元件的動作電壓介於器件的擊穿電壓和絕對最高工作電壓之間,這樣可避免它們在正常工作期間被觸發,參見圖2。

圖2

ESD單元在設計上的特性將決定其ESD擊穿電壓、最大衝擊承受能力和其折返特性。

3.

ESD和EOS的差異

當超過ESD單元鉗位元電壓的過電壓出現在IC端子上時,IC會不會損壞就取決於ESD元件被擊穿期間通過它的能量的多少。

ESD(Electro Static Discharge, 靜電釋放)和EOS(Electrical Over Stress, 電氣過應力)都是與電壓過應力有關的概念,但它們之間的差異也很明確:

- ESD的電壓很高(> 500V),持續時間相對較短(< 1µs)

- EOS的電壓相對較低(< 100V),持續時間更長一些(通常 > 1µs)

立錡科技的IC的ESD保護單元都是按照一定的標準進行設計的,這使得它們能夠承受一定的ESD脈衝能量,這些標準是關於人體模型(HBM)的JESD22-A114(其電壓值為2kV)和充電器件模型(CDM)的JESD22-C101E(其電壓值為500V)。人體模型的ESD放電過程含有極為陡峭的上升沿和大約300ns的指數式下降過程,充電器件模型的ESD放電過程呈現為極短時間的振盪脈衝,振盪週期約為4ns。比較而言,人體模型的ESD放電具有最高的能量等級。

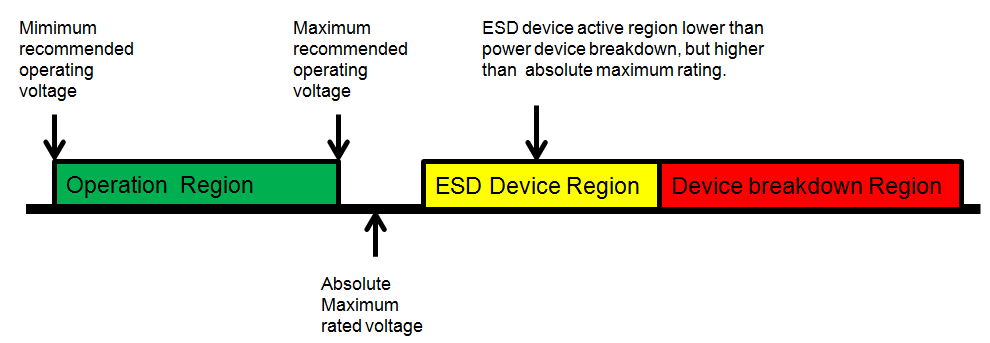

靜電放電總是在極短的時間內完成的,圖3顯示了JEDEC定義的人體模型ESD測試方法,其中的100pF電容首先被充電到一定的水準,然後通過一隻1500Ω電阻將電能釋放到受試器件上。

圖 3

由於多數受測元件的ESD保護單元的擊穿電壓都比測試電壓低很多,ESD測試的峰值電流基本上都是由測試電壓和1500Ω電阻決定的。在此波形樣板中,測試電壓為2kV,由此帶來的峰值電流為2kV/1.5k = 1.3A。RC時間常數約為150ns,因此波形下降得很快,整個過程在1µs以內。

對於2kV的ESD測試來說,釋放出來的電荷大約為0.2µC,這個資料可以被用於計算到底有多少能量在ESD期間進入ESD保護單元。例如,當ESD保護單元的擊穿電壓為27V時,2kV的人體模型ESD放電脈衝在其中釋放的能量大約為0.2µC*27V = 5.4µJ。如果是進行4kV的ESD放電測試,這個值就會翻倍到大約10.8µJ。

當持續時間更長的EOS事件發生時,衝擊ESD保護單元的能量就會更多,常常超出ESD保護單元的最大衝擊能量承受能力,這樣就會在ESD保護單元中積累太多的熱量,最終導致嚴重的毀滅性結果。通常情況下,晶片中支撐ESD保護單元的其他部分也會連帶著一起受損。

4.

由於輸入電壓太高造成IC失效的案例

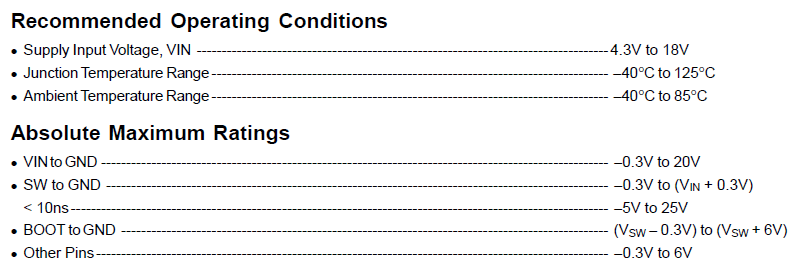

為了展示實際IC輸入端的應力限制,我們來探討一下RT7285CGE,這是一款18V耐壓的ACOT架構Buck轉換器,額定負載能力為1.5A,採用SOT-23-6封裝,它的規格書列出了下述的推薦工作條件和絕對最大額定值資料:

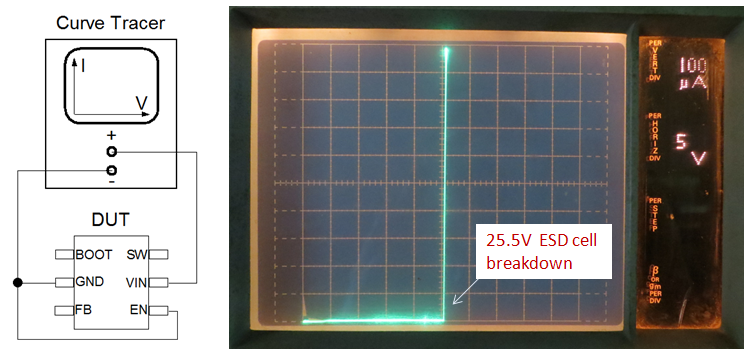

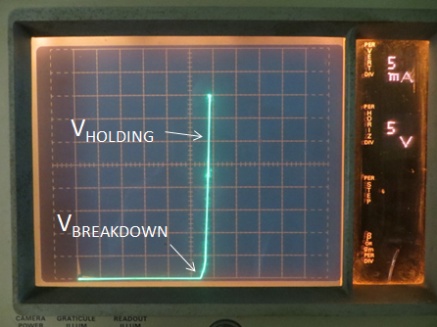

輸入端ESD保護單元的擊穿電壓應該高於上述的絕對最大額定值資料20V。為了測定實際的資料,我們可以使用I/V曲線測試儀,它應該和IC的VIN和GND連接起來。當我們這樣做的時候,IC的使能端應當和GND連接以使IC保持在關機狀態。將曲線測試儀的縱軸設定為100µA/div,同時設定其功率限制為0.5W。讓水準軸的電壓緩慢增加,最後會看到波形在電壓大約為25.5V的地方突然上升,這意味著RT7285C VIN端的ESD保護單元的擊穿電壓為這個值。由於曲線測試儀的功率是受到限制的,流過ESD保護單元的電流不會太大(< 1mA),這樣的測試不容易對IC造成損害。參見圖4。

圖4

由於ESD保護單元的擊穿特性是很陡峭的限幅狀態,超過其限幅水準的任何輸入電壓很容易就會導致大電流的出現,並且會在ESD單元中產生巨大的功耗,這將快速導致毀滅性的效果。假如我們在測試中加大曲線測試儀的電流設定和功率限制值,很容易就可以將ESD單元毀掉,我們在此時將看到擊穿特性的突然坍塌,此後,該器件將在VIN-GND之間表現為低阻特性。

(在連續模式設定中,曲線測試儀的脈衝週期很長,大約為4ms,這將在大電流測試中快速導致高能量狀態。)

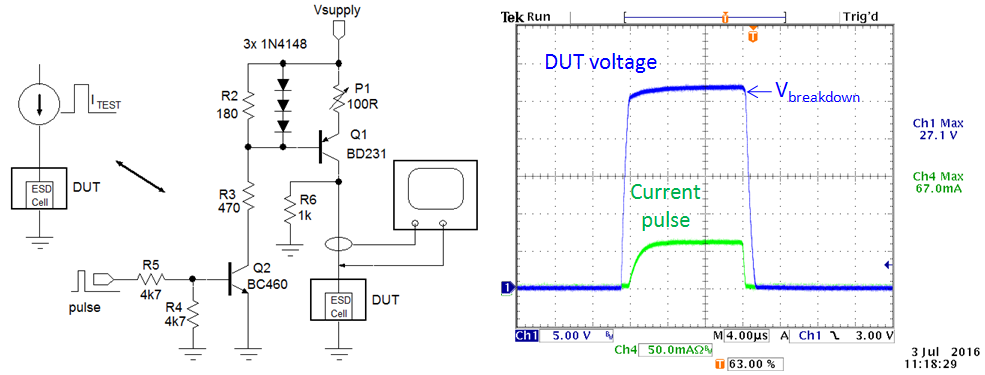

通過像圖5那樣將脈衝電流施加給受試器件,我們有可能將ESD保護單元的失效點更精確地測量出來。測量中所用的電源電壓需要高於ESD保護單元的擊穿電壓,電流脈衝的寬度和電流的幅度可以通過精確的調節以尋找到ESD保護單元在不同電流水準和不同脈衝持續時間下的不同的失效點。

圖5

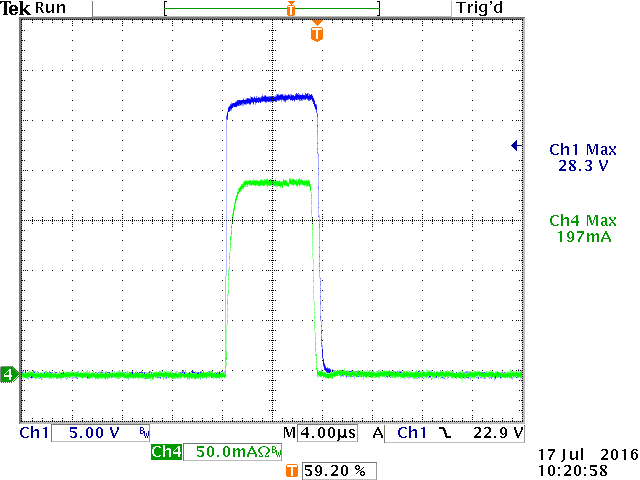

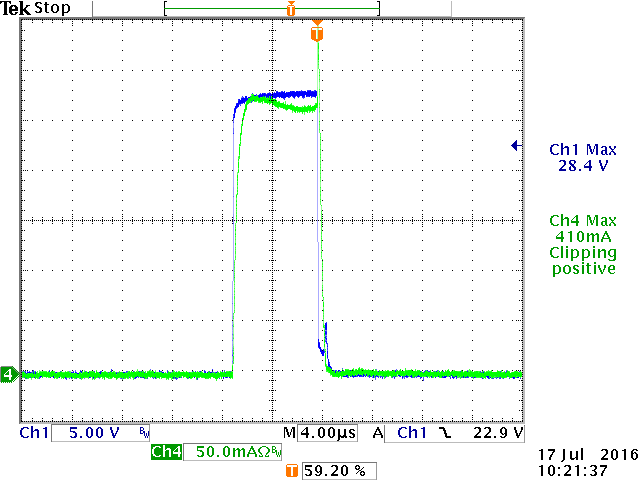

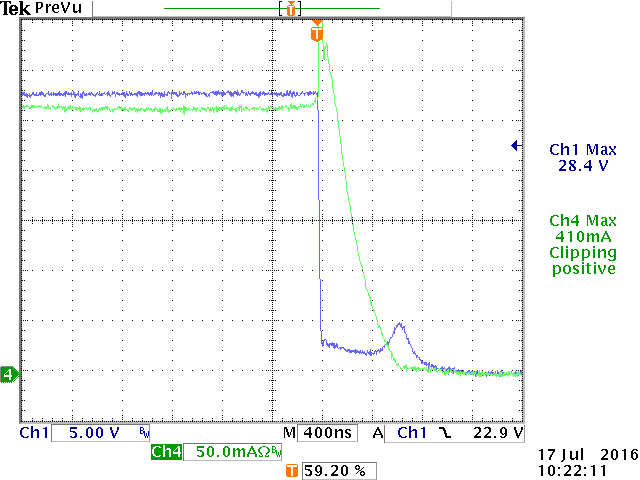

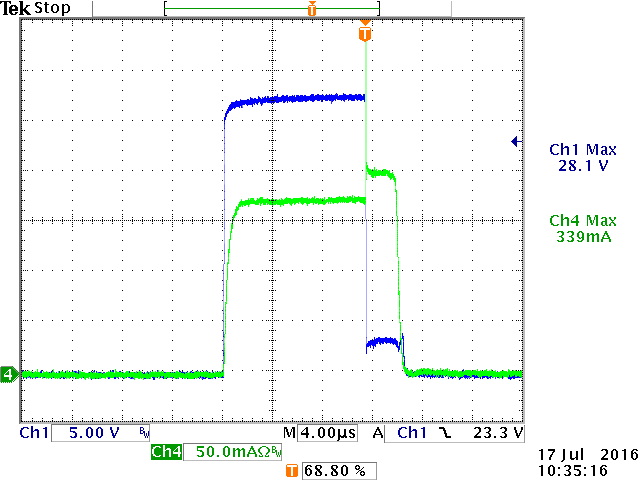

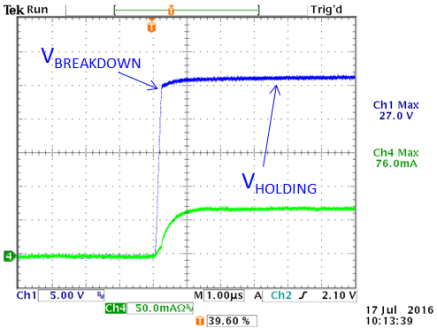

圖6給出示在25°C環境溫度下對RT7285C用電流脈衝進行擊穿測試的波形。

|

電流= 197mA, Δt = 7µs

沒有失效

|

電流= 268mA, Δt = 6.2µs

在脈衝結尾處失效

|

放大顯示的失效點,VESD降低到約3V

|

|

|

|

|

|

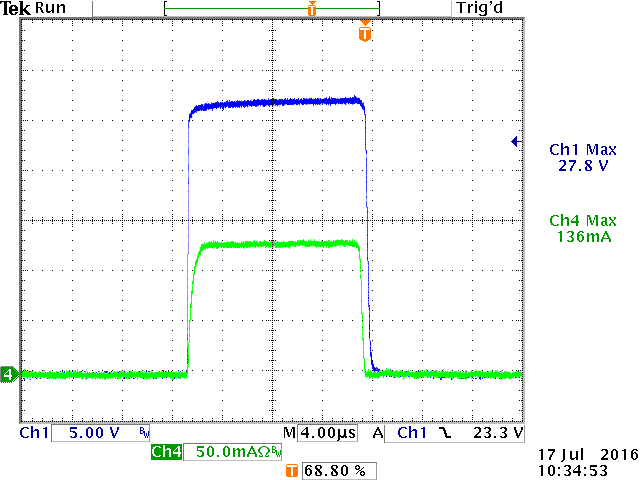

電流= 136mA, Δt = 14µs

沒有失效

|

電流= 175mA, Δt = 11.1µs

在脈衝結尾處失效

|

放大顯示的失效點,VESD降低到約3V

|

|

|

|

|

圖6

從失效發生的測試波形中,ESD單元能夠承受的最大衝擊能量可以被計算出來:當用6µs的268mA脈衝(7.6W峰值功率)時,造成器件失效的衝擊能量為47µJ;當用11µs的175mA脈衝(4.9W峰值功率)時,造成器件失效的衝擊能量大約是55µJ。造成器件失效的衝擊能量與器件的溫度是高度相關的,溫度越高,能夠造成失效的衝擊能量也越少。無論如何,在這種EOS測試中造成器件失效的能量總是明顯高於普通的人體模型ESD測試中的能量。

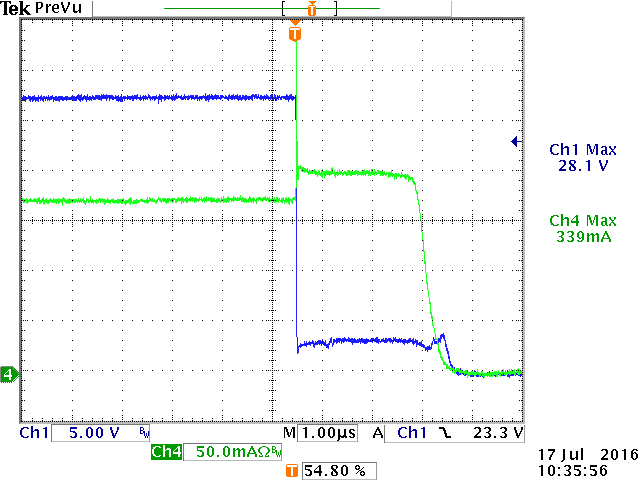

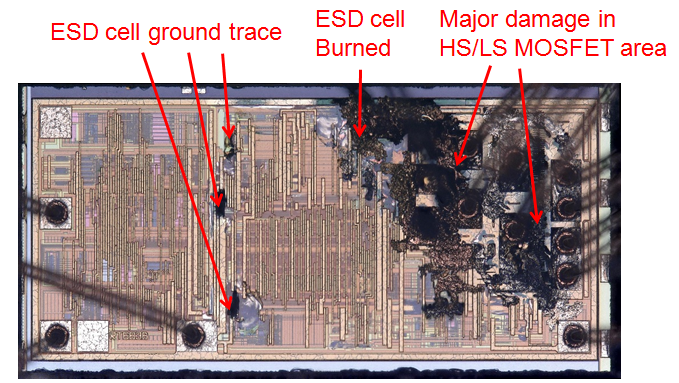

圖7顯示的是將上述測試中失效了的器件打開以後看到的景象,ESD單元顯示出燒毀了的痕跡,ESD單元與地線之間的連接路徑上也出現了燒痕。另外,與ESD單元臨近的上橋MOSFET區域也顯示出一些受損的痕跡。所有的跡象都在表明ESD單元區域受到了嚴重的熱損傷。

圖7

需要注意的是,上面的這些輸入電壓過應力都是在IC處於不工作的模式下加上去的,此過程中只有ESD單元處於活動狀態,最大電流也受到了限制。因此,矽晶片所受到的損傷也是相對不算大的。

5.

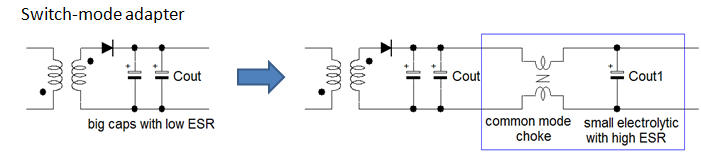

電源熱插拔導致的輸入端過應力

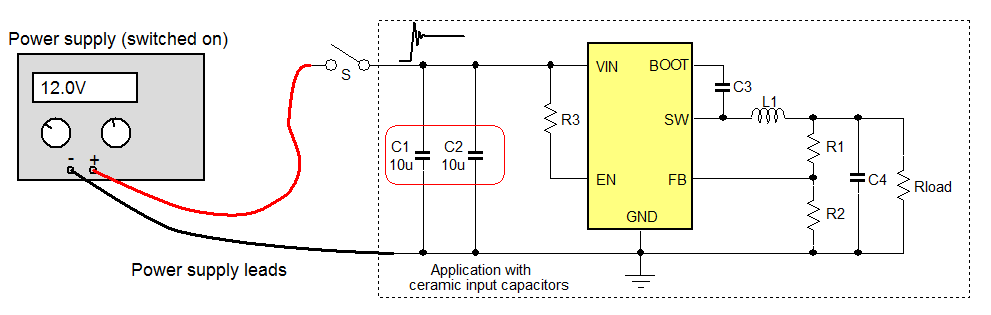

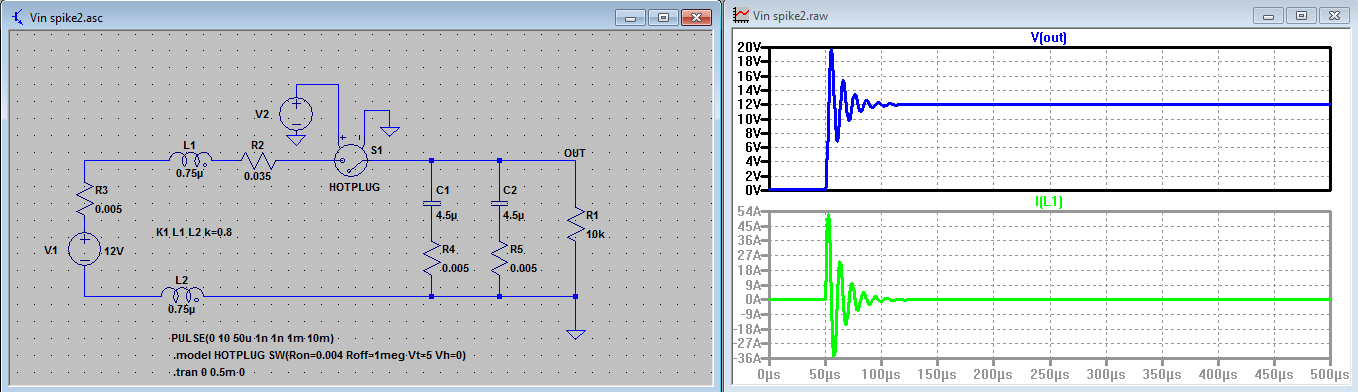

一種造成電源IC輸入端受到EOS衝擊的常見原因是電源的熱插拔事件,這種事件發生在處於開機狀態的電源被引入一個系統的時候。這種系統的輸入端通常含有低ESR的陶瓷輸入電容,它們與電源引線的電感一起發生諧振,可以導致高壓振盪信號的出現。圖8顯示的就是這樣的場景,其中的電源是開著的,有兩根引線將電源接入應用系統,其中的開關S用於類比熱插拔的行為。

圖8

出現在系統輸入端的電壓振盪信號的幅度與很多因素有關:電源供應器的內阻,引線的電阻和電感量,開關S的電阻,輸入電容C1、C2的電容量和它們的ESR的大小。

作為一個例子,我們假設12V電源供應器具有很大的輸出電容,電源引線的長度為1.2m並且具有很低的電阻,開關S的阻抗也是很低的,C1、C2是10µF/25V X5R 1206的MLCC。

電源引線的總電感大約為1.5µH,包括連接器在內其電阻約為10mΩ。兩隻電容在12V直流偏置下的實際總容量約為9µF,而且它們各自的ESR約為5mΩ。

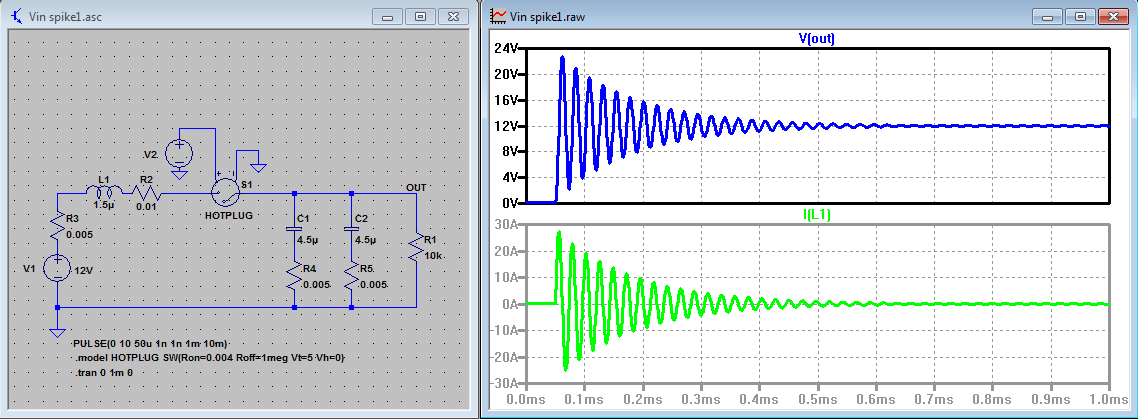

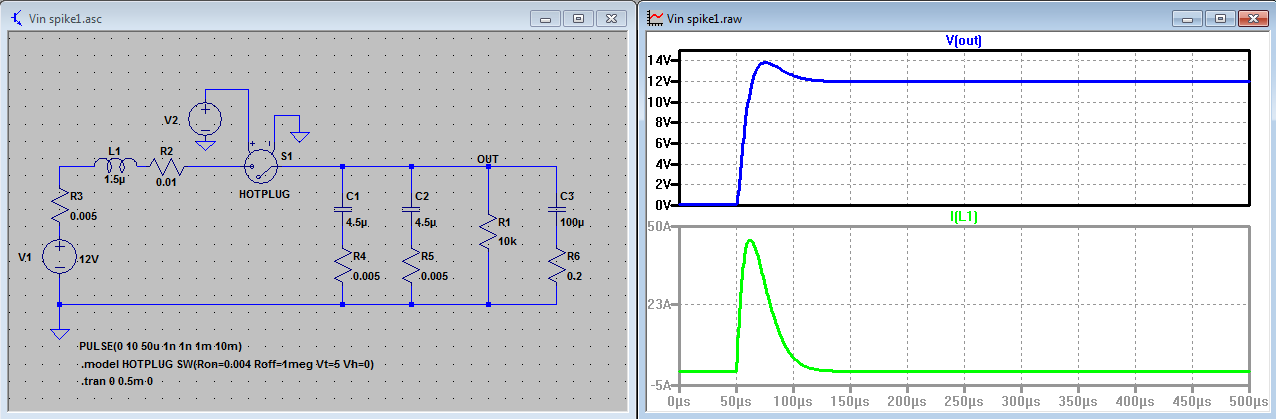

圖9顯示了熱插拔事件發生在這樣的輸入電路時的振盪過程的模擬結果。

圖9

從模擬結果可以看到,這樣的熱插拔過程導致的輸入電流高達大約30A,由引線電感和輸入電容導致的電壓振盪波形的峰值幾乎可以達到直流輸入電壓的2倍。

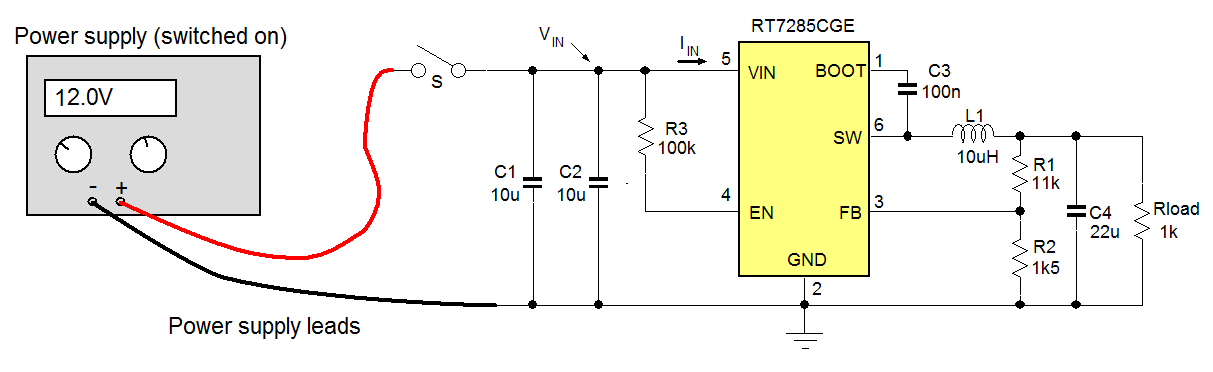

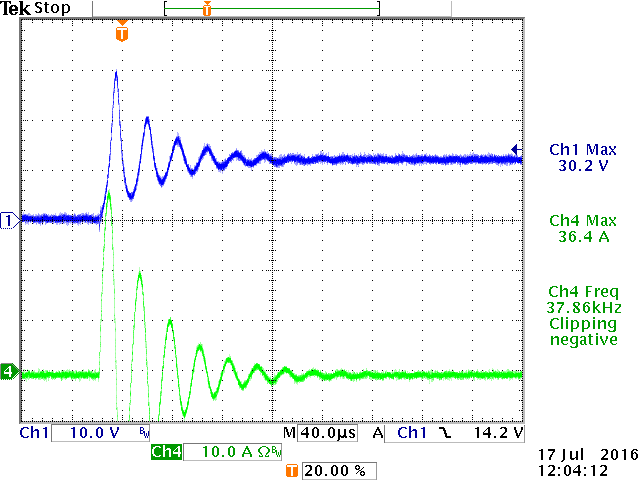

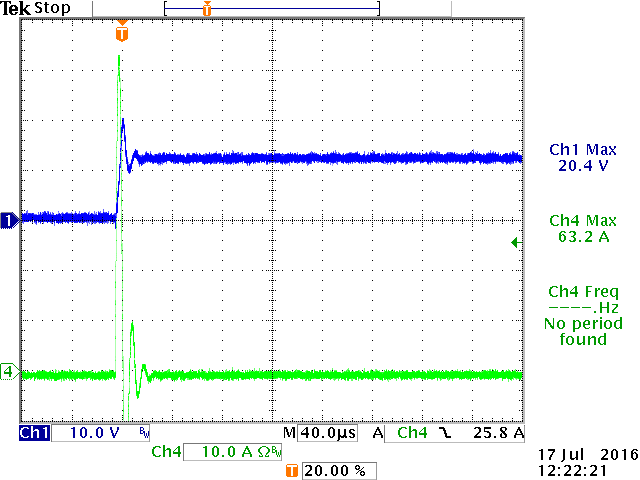

圖10顯示的是對同樣的電路進行熱插拔測試的情形,其中的開關S被換成了MOSFET,該MOSFET是用脈衝發生器驅動的,目的是讓熱插拔的動作變成是穩定的,同時也是可以重複的。

圖10

測試的結果顯示在圖11的左側:

圖11

從中可以看到,實際的熱插拔事件導致了比理論上更高的振盪電壓峰值,這是由於MLCC輸入電容在直流偏置電壓下的電容量的非線性變化導致的,它的這種特性在圖中的右側顯示出來。當電容上的電壓升高時,它的電容量會下降,對其充電的電流進入更小的電容後就會得到更高的電壓。在此案例中,12V電源的熱插拔事件能導致大約30V的最高電壓峰值。

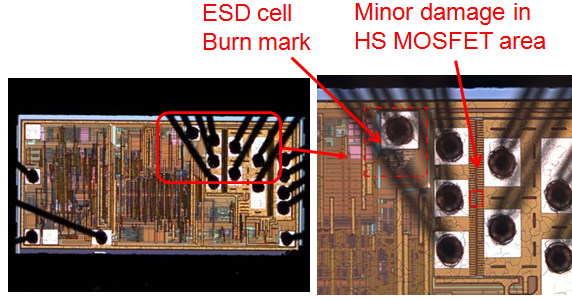

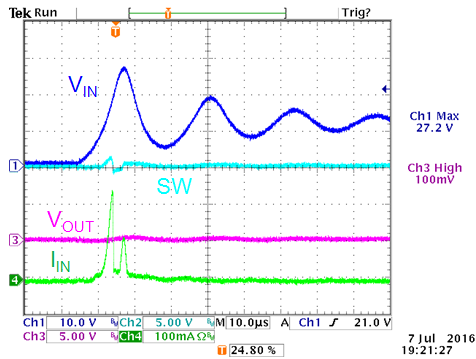

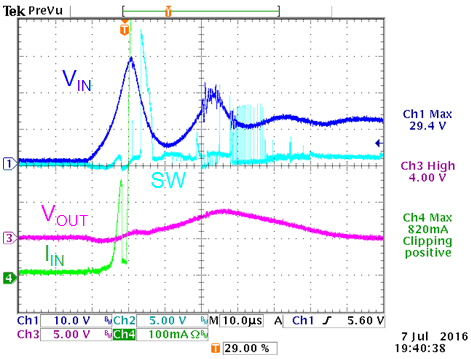

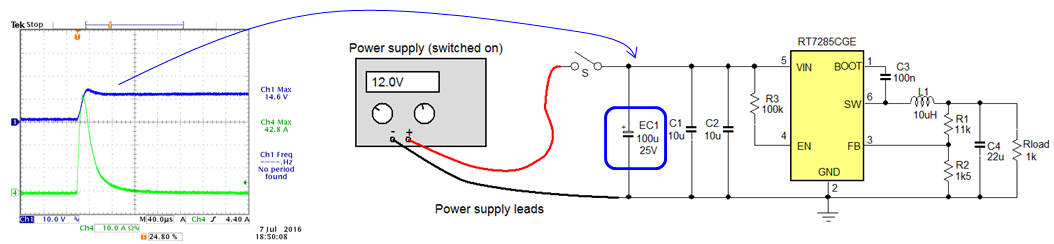

現在將同樣的熱插拔方法應用到由RT7285CGE構成的12V轉5V的標準應用電路上,再來測試此期間的IC輸入電壓和輸入電流,看看會有怎樣的表現。

通過緩慢增加直流電源的電壓,我們就能看到不同的輸入電壓峰值下導致的不同的IC輸入電流。在IC的工作模式下,IC在啟動過程中會有一個電流峰值出現,這是由IC的自舉電路開始工作造成的,我們在這裡應該將其忽略掉。在電源電壓出現尖峰期間進入IC的電流峰值出現在IC的ESD單元被擊穿的時候。

|

VSUPPLY = 11.6V,

VIN peak = 27.2V

|

VSUPPLY = 11.9V,

VIN peak = 28.4V

|

VSUPPLY = 12.1V,

VIN peak = 29.4V

|

|

|

|

|

|

ESD 單元擊穿電流:100mA

|

ESD 單元擊穿電流:532mA

|

ESD單元失效:電流失去控制,出現異常的開關動作

|

電流尖峰的持續時間大約為1.8µs,在失效前通過ESD單元的能量大約為0.6A*1.8µs*29V = 31µJ,比2kV人體模式ESD脈衝帶來的能量多5倍以上。

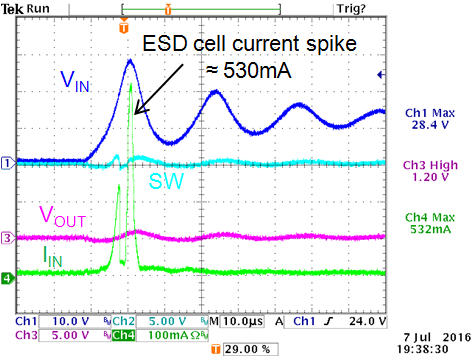

如上例,IC處於工作狀態下經受這種輸入電壓過應力時對ESD單元帶來的損傷將會大很多,這是因為沒有限制的輸入電流將導致更高的電流水準,而由此導致的功率級的功能錯誤也會帶來更嚴重的損害,通常會導致電源貫通並將MOSFET部分完全燒毀,圖12所示的就是經歷這種過應力損毀的器件在開蓋以後所看到的景象。

圖12

6.

不同類型ESD單元的擊穿特性

根據不同的IC制程和設計,ESD單元的類型也是不同的,它們各自具有獨特的個性。

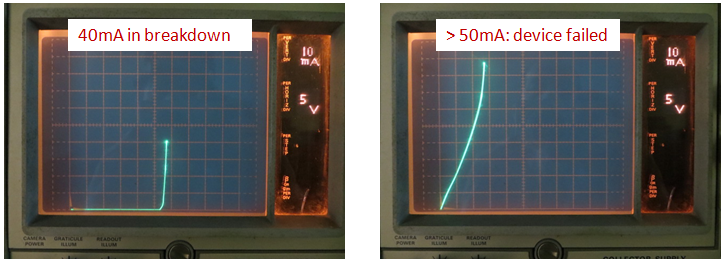

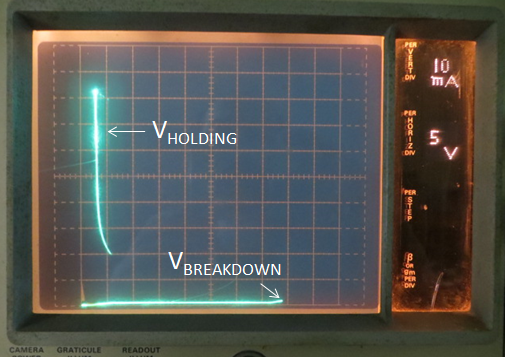

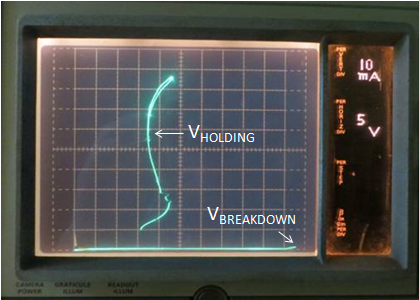

- PNP型ESD單元可將擊穿電壓點鉗制在相對固定的電壓上,其表現與齊納二極體相當。這種類型的ESD單元常用於DC-DC轉換器的輸入端保護,其表現參見圖13。

|

25V PNP ESD 單元在曲線測試儀上的表現

|

PNP ESD 單元的脈衝特性

|

PNP ESD 單元的脈衝特性的細節

|

|

|

|

|

圖13

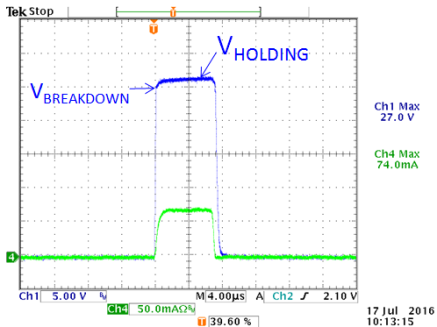

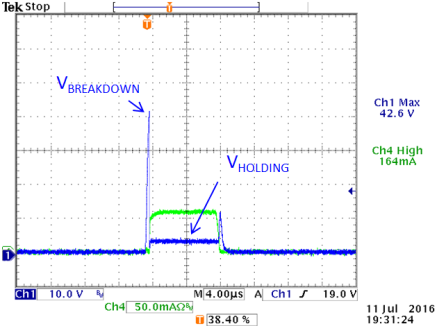

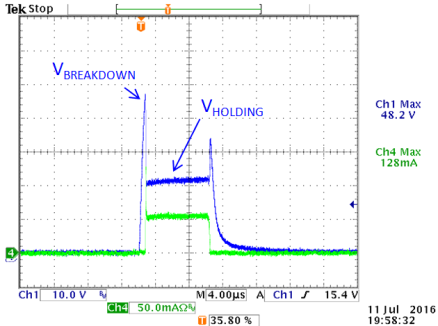

- SCR(單向可控矽整流器)型的ESD單元在擊穿後會被鉗制在很低的電壓上,表現出很猛的折返特性,其表現見圖14。

|

40V SCR ESD 單元在曲線測試儀上的表現

|

SCR ESD 單元的脈衝特性

|

SCR ESD 單元的脈衝特性的細節

|

|

|

|

|

圖14

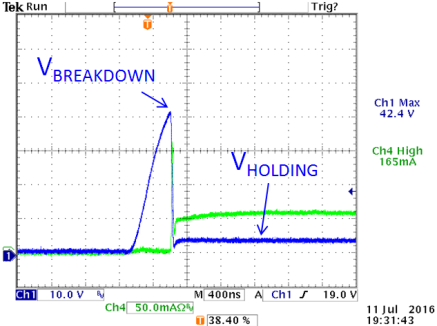

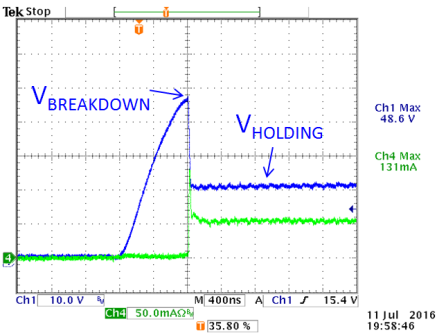

- NPN型的ESD單元在擊穿以後也表現出折返特性,但其保持電壓與SCR型ESD單元的保持電壓相比要高很多,參見圖15。

|

48V NPN ESD 單元在曲線測試儀上的表現

|

NPN ESD 單元的脈衝特性

|

NPN ESD 單元的脈衝特性的細節

|

|

|

|

|

圖15

ESD放電過程是一個電流受限的短時過程,因而SCR和NPN類型的ESD單元對高壓敏感電路的ESD保護是很有效的,因為它們都具有很低的保持電壓。但當這些類型的ESD單元在有直流電源載入的場合被觸發時,它們所具有的低維持電壓如果低於外加的直流電壓就會導致高輸入電流,從而立即造成災難性的損毀。下面的例子可供參考:

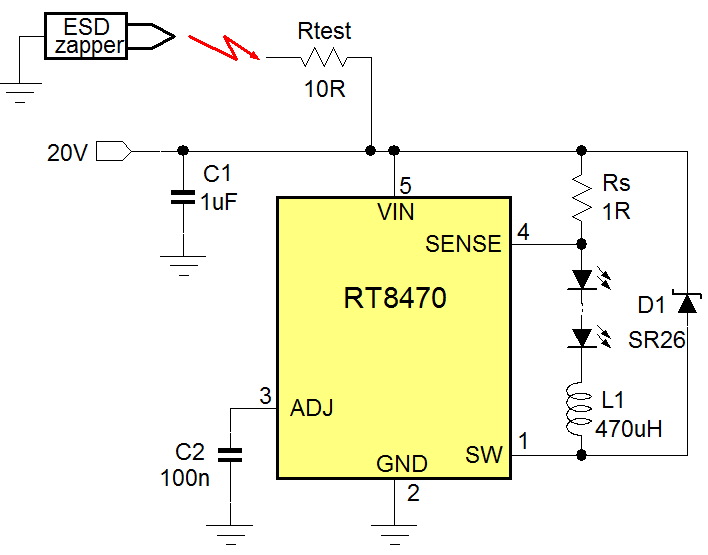

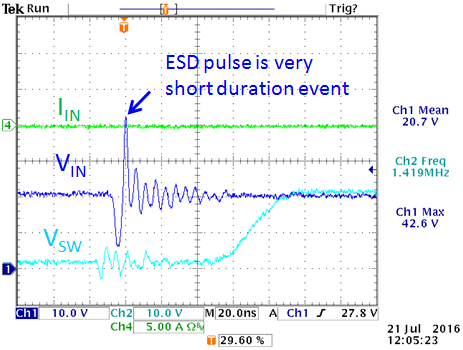

RT8470是一款老舊的Buck架構LED驅動器,它的輸入端ESD單元就是SCR類型的。當其ESD單元被出現在輸入端的短脈衝觸發時,其中的SCR就會被鎖定住,看起來就是其輸入端和地之間被短路了。圖16對此進行了示範。

|

使用ESD槍(可用氣體點火器改制)將短時電脈衝加入處於工作狀態的電源輸入端

|

放電過程在輸入端生成了短時電壓尖峰(大約5ns),此電壓尖峰還不足以觸發ESD單元動作

|

當SCR型ESD單元被觸發時,它被鎖定在低壓狀態,對電源供應器來說就相當於短路,大電流由此生成,IC被摧毀

|

|

|

|

|

圖16

7.

消除熱插拔期間電壓尖峰的措施

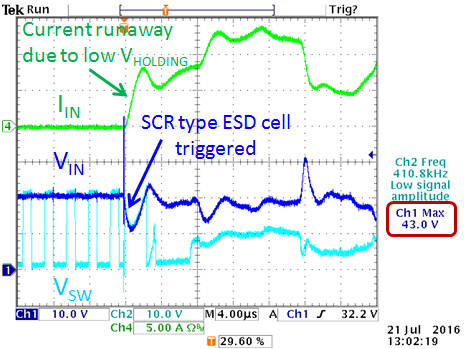

第5章已經解釋過熱插拔期間電壓尖峰發生的原因,圖17將與輸入電路有關的參數表達了出來:電源供應器的內阻Ri,電源傳輸線的電感Lwire和電阻Rwire,具有低ESR的輸入電容。

圖17

有多種方法可以降低熱插拔期間的電壓振鈴信號的幅度:

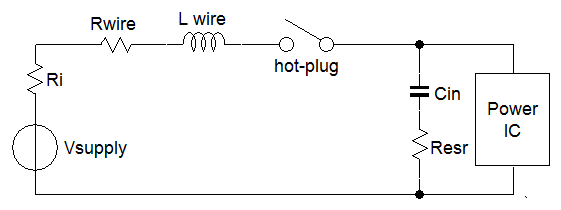

方法1:大多數電源供應器是使用了很大的輸出電容的開關模式電源適配器,這種電路的輸出阻抗很低,遇到熱插拔事件時可以快速生成大電流。如圖18那樣增加一個共模電感和一隻ESR比較高的小型電解電容,適配器的輸出阻抗就會增加,諧振過程會受到抑制。

圖18

方法2:使用較小線徑的適配器電纜來增加電纜的阻抗。為了達成好的諧振抑制效果,電纜的阻抗應該大於0.3Ω,其壞處是電纜上的壓降會增加。

方法3:增加電纜兩條線間的耦合程度。兩線間更好的耦合可以形成相反的磁場,這對諧振的抑制有幫助。圖19顯示了對75cm長、規格為18AWG的同軸電纜的類比,根據漏感測試的結果,兩線間的耦合度大概為0.8。

圖19

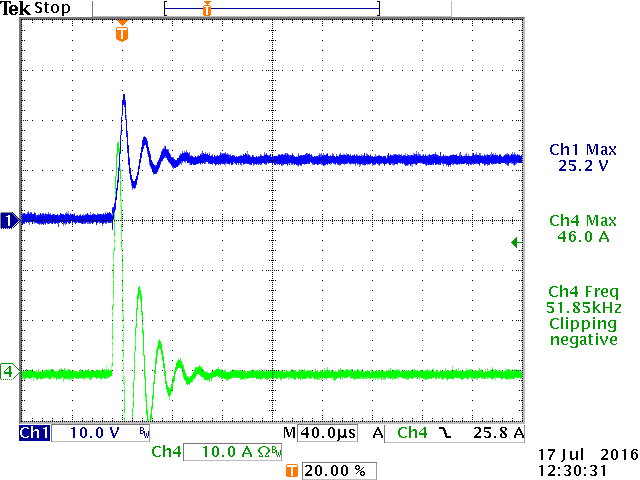

通過使用不同類型的電纜進行測量,可以確認耦合良好的線對諧振過程會有更好的抑制效果,相應的熱插拔過程所導致的電壓尖峰也更低。參見圖20。

|

75cm/12AWG/ø 2.05mm實驗室電纜,耦合度 < 0.1, Rwire = 0.008Ω

|

75cm/18AWG/ø 1.02mm雙芯電纜,耦合度 ≈ 0.3, Rwire = 0.035Ω

|

75cm/18AWG/ø 1.02mm同軸電纜,耦合度 ≈ 0.8, Rwire = 0.035Ω

|

|

|

|

|

|

|

|

|

|

F諧振 = 37kHz, V尖峰 = 30.2V

|

F諧振 = 51kHz, V尖峰 = 25.2V

|

F諧振 = 91kHz, V尖峰 = 20.4V

|

圖20

方法4:由LC電路形成的諧振可以通過給輸入電容並聯一個RC電路進行抑制,RC電路的參數可用下述方法進行計算:

RS的計算公式: 。其中LP是電纜的電感量,CIN是系統的輸入電容,ξ是希望的抑制係數。

。其中LP是電纜的電感量,CIN是系統的輸入電容,ξ是希望的抑制係數。

在前述的熱插拔案例中,LP大約是1.5µH,CIN在12V時為9µF。當我們選擇良好的抑制效果(ξ = 1)時,RS = 0.2Ω。

抑制電容CS的值必須足夠大以避免它在熱插拔造成的電流脈衝出現期間被過度充電,其電壓增量VC = IC * 1/ωC,其中的ω是LP 和 CIN的諧振頻率(測量資料大約是40kHz)。由於電流脈衝的幅度是35A,要想使充電造成的電壓增量小於2V,我們需要電容的值大於70µF。

在加入100µF和0.2Ω的RC電路後,針對上述的熱插拔案例再次進行模擬模擬,我們可以看到諧振被完全抑制住了,電壓的過沖低於2V,參見圖21所示。

圖21

在實踐中,RC抑制電路可以很容易地通過使用一隻100µF/25V的電解電容實現,它需要和陶瓷輸入電容並聯在一起。之所以這麼簡單,是因為大多數100µF的電解電容在100kHz頻率下有大約0.2Ω的ESR。

在圖22中的右側電路就在輸入端加入了100µF/25V電解電容,熱插拔試驗表明其輸入端的過沖會被完全抑制掉,不會有損毀風險再出現在IC上。

圖22

8.

其他造成電源IC輸入端EOS的原因

除了熱插拔造成的衝擊以外,還有其他一些狀況可能造成電源IC輸入端受到EOS的攻擊:

a. USB輸出端短路測試造成USB開關輸入端損毀

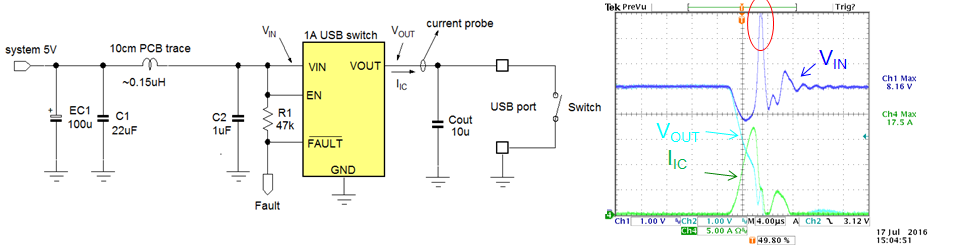

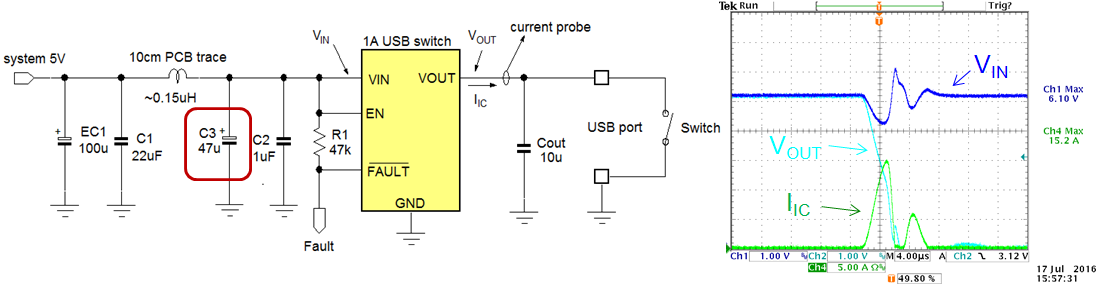

圖23顯示的是一個典型的USB開關的應用電路圖,有一個1µF的去耦電容放在靠近IC輸入端的地方,電容前面有大約10cm的銅箔路徑將它和5V主電源連接起來。

圖23

USB埠都需要進行短路測試,這個測試通過一個開關來類比,IC需要在偵測到短路以後快速將其MOSFET開關關斷。從圖23中的實例可以看到,MOSFET開關關斷的動作是有延時的,因而會有一個短時大電流流過IC之後關斷才會發生。由於輸入線有電感存在,此電感和輸入端去耦電容C2會一起發生諧振,因而可在示波器上看見輸入端出現了高壓脈衝,這很可能超過IC的最高耐壓能力並將其損毀。

為了解決這樣的可靠性隱患,用於熱插拔風險防範的類似措施可以被納入考慮範圍,因此我們要在電路中加入類似電解電容的RC抑制電路。抑制電路的參數計算方法是類似的,我們可以利用開關關斷過程的dI/dt計算電容的值。實際上,一個47µF的電解電容就可以將電壓峰值控制在大約6V上,見圖24所示。

圖24

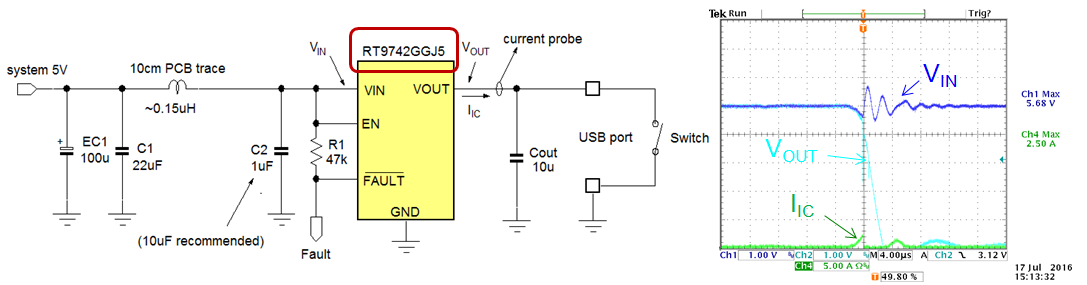

立錡科技全新的USB功率開關系列產品如RT9742已經考慮到上述的短路問題,大大縮短了對短路狀態的檢測時間,可以避免在短路測試時出現大電流。如圖25所示,雖然輸入電容仍然只有1µF,但IC輸入端在測試時仍然處於安全區間內。

圖25

b. Buck轉換器的反向偏置問題

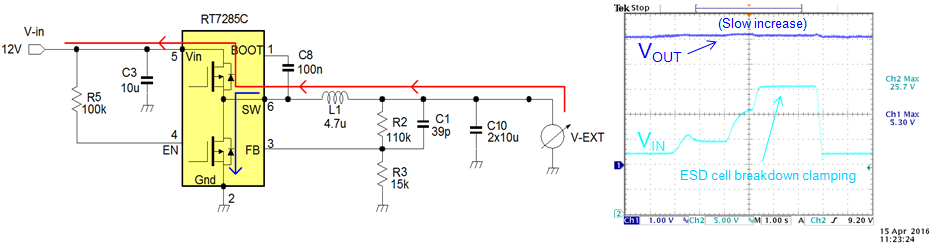

工作在強制PWM模式下的Buck轉換器如RT7285C在經由輸出端反向偏置時會表現出Boost轉換器的行為。

假如轉換器的輸出端由高於預設輸出電壓的外部電源供電時,IC內部的下橋MOSFET會從輸出端吸入電流,再與上橋MOSFET一起形成一個Boost轉換器。如圖26所示,該電路的輸出端就由一個緩慢上升的5V電源供電,它的輸入端電壓將上升並最終將其ESD單元擊穿。

圖26

像這種電源反向偏置的情況並不經常發生,但在存在電池的系統中就很容易出現。又假如在某些設計中使用了動態電壓調節技術(通過回饋網路對輸出電壓進行調節),如果輸出電容很大,又恰好遇到了輸出電壓的設定突然變低,Boost的動作就會發生了。

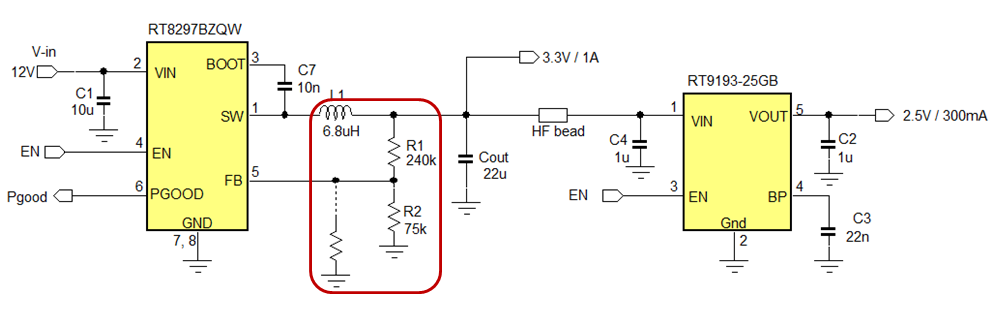

c. 回饋網路阻抗高的兩段式方案

兩段式降壓方案通常含有一級高壓元件將電壓降低到低於5V的電壓,這樣就可以用最高額定工作電壓為5.5V的器件作為第二級來使用,它可能會再為系統提供一個更低的電壓軌。

在圖27中,第一級採用17V的電流模式Buck轉換器RT8297B將12V的電壓轉換為3.3V,低壓差線性穩壓器RT9193-25再從3.3V轉出2.5V。

圖27

RT8297B是採用內部補償的Buck轉換器,回饋電阻R1的值對誤差放大器的增益會有影響,它必須被適當選擇以得到合適的交叉頻率。在此例中,輸出電容是一隻22µF的電容,這樣就需要很高的R1值來維持穩定的工作,而高阻值的R1就導致了高阻抗的回饋網路。在通常情況下,這算不上一個問題,除非你拿手去觸碰回饋網路,或者是遇到PCB存在漏電的狀況(到地的),這時候的FB端就會受到干擾,導致輸出電壓的提高,嚴重的情況下就會導致線性穩壓器的損壞。

有些電路設計者會故意用手去觸碰以完成自己的測試,他們通過用手指觸碰PCB上的不同位置來看會不會有電壓抖動的現象,從而發現走線或是高阻的敏感位置。ACOT®;架構的Buck轉換器或使用GM型誤差放大器的電流模式轉換器對回饋網路的阻抗就不太敏感,可以在這樣的應用中予以採用。

9.

用自製工具生成EOS

下面介紹一些可以自製的過應力測試工具,用它們可以分別生成脈動的電流、電場和磁場。

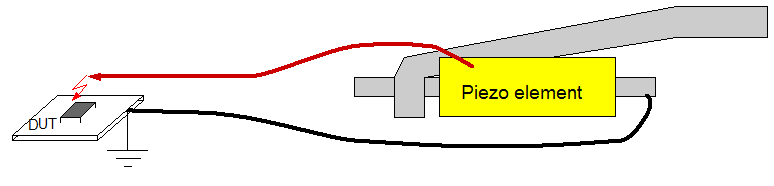

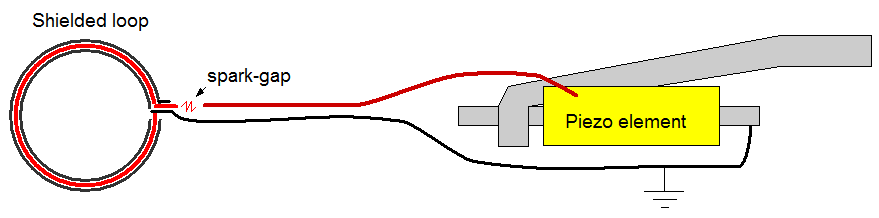

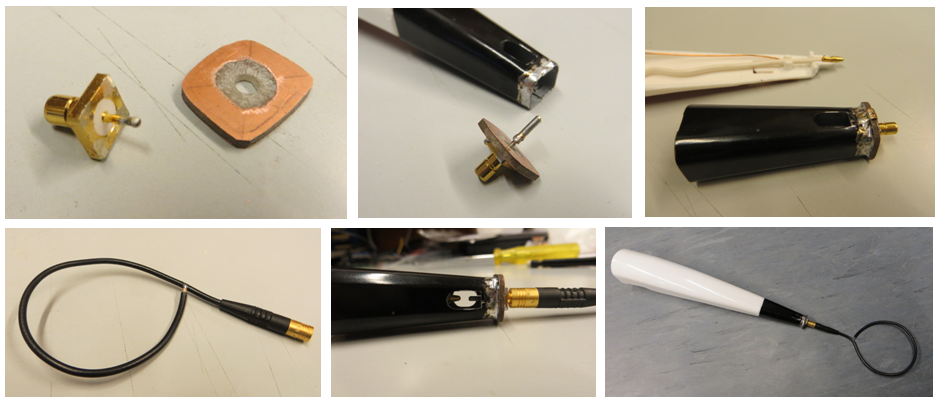

a. ESD發生器(圖28)

這款工具是用壓電式的氣體點火器改制的,這種工具不需要使用電池。

圖28

此工具可以像ESD槍一樣生成高壓脈衝,小心別把自己打著了。

下圖是製作的流程:

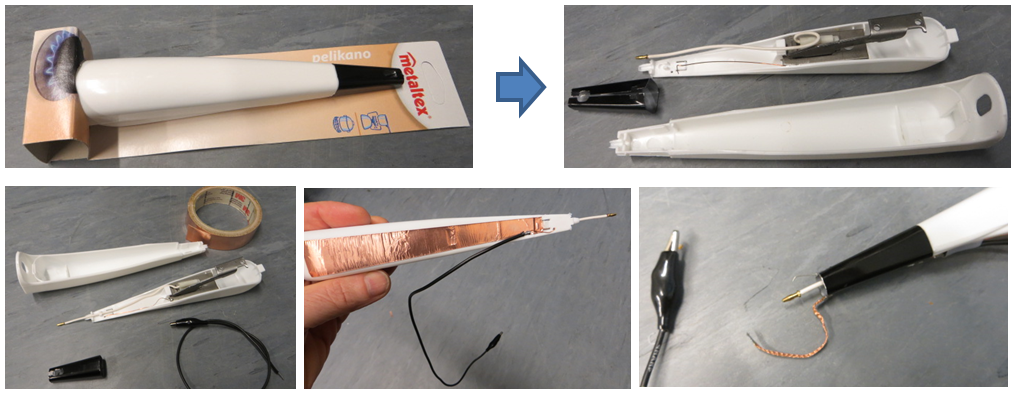

圖29

製作這個工具需要將壓電式氣體點火器拆開來進行。首先將金屬外殼取下來,把高壓線撥到外面,用銅箔把手柄蓋住,將壓電陶瓷的地與銅箔以及地線連接起來。再次裝上金屬外殼,確保它和銅箔之間連接良好。你還可以在外殼上增加一條地線以降低它和測試物件連接時的阻抗。參見圖29。

做試驗的時候不要直接對IC進行攻擊,你可以在不同的接地點之間或是電源的正極和地之間進行攻擊,也可以在電源線上串聯電阻以後再行攻擊以得到更多不同的量化效果。

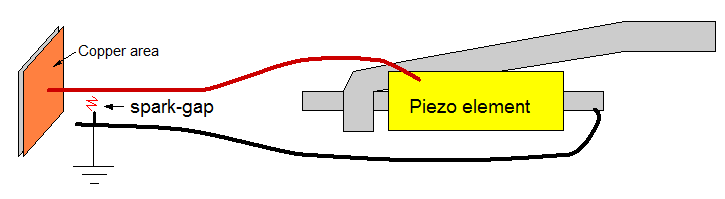

b. 脈衝電場發生器,見圖30。

圖30

這個工具可直接從ESD發生器轉變而來。將一塊銅箔和高壓節點連接起來,再在高壓節點和地之間增加一個火花隙即可形成,參見圖31。

圖31

你可以用這個工具檢查你的系統在快速變化的電場下的魯棒性,很多高阻抗的電路會受到它的影響。

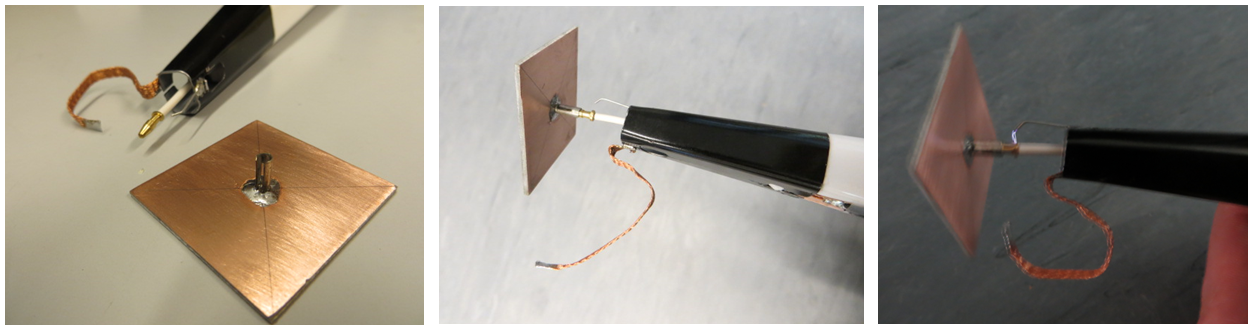

c. 脈衝磁場發生器,參見圖32。

圖32

這個工具是通過將電流脈衝送入一個線圈使之生成快速變化的磁場來形成的。

你還是可以使用壓電式點火器來製作此工具,但你這時候需要使用一個能夠固定線圈的裝置。在壓電式點火器的頂端安裝一個小型同軸連接器是比較方便的,這樣會給連接不同的線圈帶來方便。

一塊小型的雙面PCB可以用作安裝連接器的基座,然後再將PCB和金屬外殼焊接起來。你還需要增加一塊接地的銅箔,它要將氣體點火器的手柄、壓電元件的地端和金屬外殼連接在一起。

高壓線的位置需要進行調節,使之形成2~3mm的火花放電間隙。

遮罩環的製作與用於EMI測試的環形天線的製作方法是一樣的,請參考應用筆記AN045,請注意同軸線的內芯線末端要和電纜的遮罩層焊接在一起。參見圖33。

你可以用這個工具對應用中的敏感環路進行檢查,像IC的去耦回路就可以用此方法進行檢測。你也可以將線圈與鐵氧體磁芯耦合在一起將脈衝電流引入電纜中去,這很類似共模電流測量,但這時候的環形線圈變成了發送器。

需要注意的是這個工具可以生成極端糟糕的脈衝干擾,不要在敏感的數位電路附近使用它。

圖33

10. 總結

電源IC的損壞經常是由於輸入電壓過應力造成的,這在電源熱插拔導致出現過高電壓尖峰或由線路電感和低ESR陶瓷電容形成諧振時就會發生。

當電源IC輸入端的ESD單元遇到超過其能量承擔水準的衝擊能量時就會被損壞。造成IC損壞的EOS能量通常要比正常的人體模式(HBM)ESD能量高好幾倍。當ESD單元被損壞的時候,作為其承載體的矽晶圓也會受到傷害。在大多數情況下,承載體的損壞會直接導致功率級的不正常運作,引起直通短路、功率級燒毀等問題。

具有折返特性的ESD單元在被觸發以後可能保持在低於工作電壓的電壓上,這會在被觸發之後立即導致大電流的出現。

由於熱插拔事件和電源線上的諧振效應都會將電壓尖峰引入IC輸入端,因而在電源設計過程中必須對這樣的瞬態過程進行檢查,確保在任何情況下都不會在IC輸入端形成高電壓。由於ESD單元的啟動電壓總是高於器件的絕對最大額定值,應用中能夠出現的電壓就不能超過IC的絕對最大額定值,以便確保ESD單元在工作過程中不會被啟動。

參考文獻:

Fundamentals of Electromagnetic Compatibility 2nd edition, by B. Danker